PROGRAM

Registration/Information Hours

| ETS/Workshops | Registration Desk at 1st Floor |

| Monday, May 28 | 12:00-21:00 |

| Tuesday, May 29 | 08:00-20:00 |

| Wednesday, May 30 | 08:00-16:00 |

| Thursday, May 31 | 08:00-20:00 |

| Workshops Only | Registration Desk at 1st Floor |

| Thursday, May 31 | 16:00-20:00 |

| Friday, June 01 | 08:00-16:00 |

MONDAY, MAY 28, 2018

14:00 - 16:00 TSS@ETS TUTORIAL 1*: PART 1

Moderator: Paolo BERNARDI, Politecnico di Torino - ItalyZÜRICH I

-

Automotive Test for Functional Safety

Yervant ZORIAN, Synopsys - USA

14:00 - 16:00 TSS@ETS TUTORIAL 2*: PART 1

Moderator: Lorena ANGHEL, Université Grenoble Alpes - FranceZÜRICH II

-

Embedded System Security: Cryptographic Challenges and Physical Threats

Tim GÜNEYSU, Ruhr-University Bochum - Germany

16:00-16:30 Coffee Break

FOYER

16:30 - 18:30 TSS@ETS TUTORIAL 1*: PART 2

Moderator: Paolo BERNARDI, Politecnico di Torino - ItalyZÜRICH I

-

Automotive Test for Functional Safety

Yervant ZORIAN, Synopsys - USA

16:30 - 18:30 TSS@ETS TUTORIAL 2*: PART 2

Moderator: Lorena ANGHEL, Université Grenoble Alpes - FranceZÜRICH II

-

Embedded System Security: Cryptographic Challenges and Physical Threats

Tim GÜNEYSU, Ruhr-University Bochum - Germany

18:30 - 19:00 Break

FOYER

19:00 - 20:30 Welcome Reception

FOYER

*The TSS@ETS Tutorials of Monday afternoon are accessible to all ETS attendees with a full registration. The complete TSS program can be found here.

TUESDAY, MAY 29, 2018

8:30 - 9:00 OPENING SESSION

ZÜRICH I+II

-

Welcome Message

Rolf DRECHSLER, University of Bremen, DFKI GmbH - Germany, ETS'18 General Chair

Stephan EGGERSGLUESS, Mentor, A Siemens Business - Germany, ETS'18 General Chair -

Program Introduction

Bernd BECKER, University of Freiburg - Germany, ETS'18 Program Chair -

Symposium Information

Sebastian HUHN, University of Bremen, DFKI GmbH - Germany, ETS'18 Local & Financial Chair -

ETS'17 Best Paper Award

Zebo PENG*, Régis LEVEUGLE‡, *Linköping University - Sweden, ‡TIMA Laboratory - France, ETS'17 Award Chairs -

Test Technology Technical Council (TTTC) Awards

Yervant ZORIAN, Synopsys - USA, TTTC President of Board

-

Making the Autonomous Dream Work

Riccardo MARIANI, Intel Corporation - Italy

10:00 - 11:00 Coffee Break

FOYER

10:00 - 11:00 TABLE-TOP DEMOS

Moderator: Sebastian HUHN, University of Bremen, DFKI GmbH - GermanyFOYER

-

Automotive Microcontroller Development at Infineon

Daniel TILLE, Infineon Technologies - Germany

-

Ridgetop' solutions for test cost reduction and device characterization

Hans MANHAEVE, Ridgetop Europe - Belgium

-

Tessent® - The DFT market leader

Kan THAPAR, Mentor, A Siemens Business - UK

10:00 - 11:00 POSTER SESSION - PhD Contest

FOYER

| Moderators: | Said HAMDIOUI, TU Delft - The Netherlands |

| Matthias SAUER, University of Freiburg - Germany |

11:00 - 12:30 SESSION 1A: Security and Trust

11:00 - 12:30 SESSION 1A: Security and Trust ZÜRICH III

| Moderators: | Ilia POLIAN, University of Stuttgart - Germany Johanna SEPULVEDA, Technical University of Munich - Germany |

-

Detection of IJTAG Attacks Using LDPC-based Feature Reduction and Machine Learning

Xuanle REN‡*, Ronald BLANTON‡, Vitor TAVARES*, ‡Carnegie Mellon University - USA, *University of Porto - Portugal -

Online Prevention of Security Violations in Reconfigurable Scan Networks

Ahmed ATTEYA‡, Michael KOCHTE‡, Matthias SAUER*, Pascal RAIOLA*, Bernd BECKER*, Hans-Joachim WUNDERLICH‡, ‡University of Stuttgart - Germany, *University of Freiburg - Germany -

Locking of Biochemical Assays for Digital Microfluidic Biochips

Jack TANG‡, Sukanta BHATTACHARJEE‡, Mohamed IBRAHIM*, Krishnendu CHAKRABARTY*, Ramesh KARRI‡, ‡New York University - USA, *Duke University - USA

11:00 - 12:30 SESSION 1B: ETS2 1

ZÜRICH II

| Moderators: | René SEGERS, ReSeCo - The Netherlands |

| Zebo PENG, Linköping University - Sweden |

- Emerging IEEE Standards for DFT of Mixed-Signal ICs

11:00 - 12:30 SESSION 1C: Vendor Session 1

Moderator: Grzegorz MRUGALSKI, Mentor, A Siemens Business - PolandZÜRICH I

-

Fault Simulation: Applications and Challenges

Mehdi DEHBASHI‡, Frederico FERLINI*, ‡Infineon Technologies - Germany, * Cadence Design System - Germany -

IP for Functional Safety Applications

Pete HARROD, Arm Ltd. - UK -

Test technology & the real world - addressing the challenge of ASIL-D

Vivek CHICKERMANE, Cadence Design Systems - USA

12:30 - 14:00 Lunch Break

FOYER

14:00 - 15:30 SESSION 2A: Analog, Mixed-Signal and RF

14:00 - 15:30 SESSION 2A: Analog, Mixed-Signal and RF ZÜRICH III

| Moderators: | Jochen RIVOIR, Advantest - Germany Hans KERKHOFF, University of Twente - The Netherlands |

-

ADC Test Methods using an impure Stimulus: a Survey

Jan SCHAT, NXP Semiconductors - Germany -

Measuring mixed-signal test stimulus quality

Stephen SUNTER, Krzysztof JURGA, Mentor, A Siemens Business - Canada, Poland -

Assisted test design for non-intrusive machine learning indirect test of millimeter-wave circuits

Florent CILICI, Manuel BARRAGAN, Salvador MIR, Estelle LAUGA-LARROZE, Sylvain BOURDEL, Université Grenoble Alpes - France

14:00 - 15:30 SESSION 2B: ETS2 2

ZÜRICH II

| Moderators: | René SEGERS, ReSeCo - The Netherlands Zebo PENG, Linköping University - Sweden |

- Data sharing in the IC supply chain, a good or a bad idea?

14:00 - 15:30 SESSION 2C: Vendor Session 2

Moderator: Hans MANHAEVE, Ridgetop Europe - BelgiumZÜRICH I

-

Dependability for Safety Critical Applications: AMS Extensions

Vladimir ZIVKOVIC, Art SCHALDENBRAND, Cadence Design Systems - UK -

Is SPC obsolete for real time monitoring in electronics manufacturing?

Vidas GRONAS, Virinco AS - Norway -

What's new with Tessent MemoryBIST

Martin KEIM, Mentor, A Siemens Business - USA

15:30 - 16:00 Coffee Break

FOYER

Moderator: Daniel TILLE, Infineon Technologies - Germany

Special Session 1: Functional Safety and Test

-

From customer requirements to safe silicon development and test

Jens ROSENBUSCH, Infineon Technologies - Germany -

Functional Safety - challenges and chances

Mario TRAPP, Fraunhofer Institute - Germany -

Driverless-cars: the holy grail of autonomous systems' safety

Rakshith AMARNATH, Robert Bosch GmbH - Germany

16:00 - 17:30 SESSION 3B: ETS2 3

ZÜRICH II

| Moderators: | René SEGERS, ReSeCo - The Netherlands |

| Zebo PENG, Linköping University - Sweden |

- Data sharing in the IC supply chain, a good or a bad idea?

16:00 - 17:30 TTTC's E. J. McCluskey Doctoral Thesis Award - ETS Semi-Finals

ZÜRICH I

| Moderators: | Said HAMDIOUI, TU Delft - The Netherlands Matthias SAUER, University of Freiburg - Germany |

17:30 - 18:00 Break

FOYER

18:00 - 19:30 SESSION 4A: Panel 1: Wine & Cheese Panel

18:00 - 19:30 SESSION 4A: Panel 1: Wine & Cheese PanelZÜRICH I+II

| Organizers: | Jeff REARICK, AMD - USA Mehdi TAHOORI, Karlsruhe Institute of Technology - Germany |

The Future of Test (Community): Ask the Experts

WEDNESDAY, MAY 30, 2018

Moderator: Sudhakar REDDY, University of Iowa - USA

10:30 - 12:00 SESSION 5A: System Control and Test

10:30 - 12:00 SESSION 5A: System Control and Test

13:30 - 15:00 SESSION 6A: Panel 2

Organizer and Moderator: Xinli GU, Huawei Technologies - USA

13:30 - 15:00 SESSION 6A: Panel 2

Organizer and Moderator: Xinli GU, Huawei Technologies - USA

Is Machine Learning Really Useful for Test & Reliability?

-

Automotive ICs - the Key Driver of Innovation in Test

Janusz RAJSKI, Mentor, A Siemens Business - USA

9:30 - 10:30 Coffee Break

FOYER

9:30 - 10:30 TABLE-TOP DEMOS

Moderator: Sebastian HUHN, University of Bremen, DFKI GmbH - GermanyFOYER

-

Automotive Microcontroller Development at Infineon

Daniel TILLE, Infineon Technologies - Germany

-

Ridgetop' solutions for test cost reduction and device characterization

Hans MANHAEVE, Ridgetop Europe - Belgium

-

Tessent® - The DFT market leader

Kan THAPAR, Mentor, A Siemens Business - UK

9:30 - 10:30 POSTER SESSION

Moderator: Stelios NEOPHYTOU, University of Nicosia - CyprusFOYER

-

Covering Undetected Standard Transition Fault Sites with Optimistic Unspecified Transition Faults under Multicycle Tests

Irith POMERANZ, Purdue University - USA -

Covering Hard-to-Detect Defects by Thermal Quorum Sensing

Po-Yao CHUANG‡, Cheng-Wen WU‡, Harry H. CHEN*, ‡National Tsinghua University - Taiwan, *MediaTek Inc. - Taiwan -

ReiNN: Efficient Error Resilience in Artificial Neural Networks using Embedded Consistency Checks

Sujay PANDEY, Suvadeep BANERJEE, Abhijit CHATTERJEE, Georgia Institute of Technology - USA -

Fault-Detection-Strengthened Method to Enable the POST for Very-Large Automotive MCU in Compliance with ISO26262

Senling WANG‡, Yoshinobu HIGAMI‡, Hiroshi TAKAHASHI‡, Hiroyuki IWATA*, Yoichi MAEDA*, Jun MATSUSHIMA*, ‡Ehime University - Japan, *Renesas Electronics Corporation - Japan -

Variation-Tolerant Path Delay Order Encoding for HT Detection

Xiaotong CUI‡, Kaijie WU*, Ramesh KARRI*, ‡Chongqing University - China, *New York University - USA -

Extending Post-Silicon Coverage Measurement Using Time-Multiplexed FPGA Overlays

Fatemeh ESLAMI, Eddie HUNG, Steven J.E. WILTON, University of British Columbia - Canada

10:30 - 12:00 SESSION 5A: System Control and Test

10:30 - 12:00 SESSION 5A: System Control and Test ZÜRICH III

| Moderators: |

Liviu MICLEA, Technical University Cluj-Napoca - Romania Rene KRENZ-BAATH, Hochschule Hamm-Lippstadt - Germany |

-

IEEE Std P1838's Flexible Parallel Port and its Specification with Google's Protocol Buffers

Yu LI‡, Ming SHAO‡, Hailong JIAO*, Adam CRON♢, Sandeep BHATIA~, Erik Jan MARINISSEN♤*, ‡KU Leuven - Belgium, *TU Eindhoven - The Netherlands, ♢Synopsys - USA, ~Google - USA, ♤IMEC - Belgium -

A Software Reconfigurable Assertion Checking Unit for Run-Time Error Detection

Yumin ZHOU, Sebastian BURG, Oliver BRINGMANN, Wolfgang ROSENSTIEL, University of Tübingen - Germany -

Towards the Formal Verification of Security Properties of a Network-on-Chip Router

Johanna SEPULVEDA‡, Damian ABOUL-HASSAN‡, Georg SIGL‡, Bernd BECKER*, Matthias SAUER*, ‡Technical University of Munich - Germany, *University of Freiburg - Germany

10:30 - 12:00 SESSION 5B: Embedded Tutorial 1

Moderator: Sybille HELLEBRAND, University of Paderborn - GermanyZÜRICH II

-

Design of Fault-Tolerant Neuromorphic Computing Systems

Krishnendu CHAKRABARTY, Duke University - USA, Yu WANG, National Tsinghua University - China

10:30 - 12:00 TTTC's E. J. McCluskey Doctoral Thesis Award - ETS Semi-Finals

ZÜRICH I

| Moderators: | Said HAMDIOUI, TU Delft - The Netherlands Matthias SAUER, University of Freiburg - Germany |

12:00 - 13:30 Lunch Break

FOYER

13:30 - 15:00 SESSION 6A: Panel 2

13:30 - 15:00 SESSION 6A: Panel 2 ZÜRICH I+II

Is Machine Learning Really Useful for Test & Reliability?

15:00 - 15:30 Break

FOYER

15:30 - 23:00 Social Event

THURSDAY, MAY 31, 2018

Moderator: Rolf DRECHSLER, University of Bremen, DFKI GmbH - Germany

11:00 - 12:30 SESSION 7A: Latches and Memories

11:00 - 12:30 SESSION 7A: Latches and Memories

Special Session 2: Test Technologies for Safety-Critical Automotive ICs

14:00 - 15:30 SESSION 8A: Test for Advanced Fault Models

14:00 - 15:30 SESSION 8A: Test for Advanced Fault Models

Special Session 3: Device Aging: A Security and Reliability Concern

-

Model-based Avionic Systems Testing for the Airbus Family

Jan PELESKA, University of Bremen - Germany

10:00 - 11:00 Coffee Break

FOYER

10:00 - 11:00 TABLE-TOP DEMOS

Moderator: Sebastian HUHN, University of Bremen, DFKI GmbH - GermanyFOYER

-

Automotive Microcontroller Development at Infineon

Daniel TILLE, Infineon Technologies - Germany

-

Ridgetop' solutions for test cost reduction and device characterization

Hans MANHAEVE, Ridgetop Europe - Belgium

-

Tessent® - The DFT market leader

Kan THAPAR, Mentor, A Siemens Business - UK

10:00 - 11:00 POSTER SESSION

Moderator: Mario SCHOELZEL, IHP - GermanyFOYER

-

Methodology for Determining the Influencing Factors of Lifetime Variation for Power Devices

Ciprian V. POP‡*, Andi BUZO*, Georg PELZ*, Horia CUCU‡, Corneliu BURILEANU‡, ‡University Politehnica of Bucharest - Romania, *Infineon Technologies - Germany -

On No-Reference On-Line Error-Tolerability Testing for Videos

Tong-Yu HSIEH, Shang-En CHAN, Chi-Hsuan HO, National Sun Yat-sen University - Taiwan -

An Efficient Fault-Tolerant Valve-Based Microfluidic Routing Fabric for Single-Cell Analysis

Yasamin MORADI‡, Krishnendu CHAKRABARTY*, Ulf SCHLICHTMANN‡, ‡Technical University of Munich - Germany, *Duke University - USA -

Recycled IC Detection through Coarse-Grained Aging Sensor

Daniele ROSSI‡, Vasileios TENENTES*, Saqib KHURSHEED♢, Sudhakar M. REDDY♤ ‡University of Hertfordshire - UK, *University of Southampton - UK, ♢University of Liverpool - UK, ♤University of Iowa - USA -

Automatic Generation of In-Circuit Tests for Board Assembly Defects

Harm VAN SCHAAIJK‡*, Martien SPIERINGS‡, Erik Jan MARINISSEN*♢, ‡Prodrive Technologies - The Netherlands, *TU Eindhoven - The Netherlands, ♢IMEC - Belgium -

A Zero-Timing Overhead Mitigation Approach of SET on Flash-based FPGAs

Sarah AZIMI, Boyang DU, Luca STERPONE, Politecnico di Torino - Italy

11:00 - 12:30 SESSION 7A: Latches and Memories

11:00 - 12:30 SESSION 7A: Latches and Memories ZÜRICH III

| Moderators: | Vivek CHICKERMANE, Cadence Design Systems - USA Frank SILL TORRES, DFKI GmbH - Germany |

-

The Impact of Production Defects on the Soft-Error Tolerance of Hardened Latches

Stefan HOLST, Ruijun MA, Xiaoqing WEN, Kyushu Institute of Technology - Japan -

Modeling and Testing Comparison Faults of Memristive Ternary Content Addressable Memories

Li-Wei DENG, Jin-Fu LI, Yong-Xiao CHEN, National Central University - Taiwan -

Sense Amplifier Offset Characterisation for Low-Voltage SRAM Application in 65 nm

Dhruv PATEL‡*, Derek WRIGHT‡, Manoj SACHDEV‡, ‡University of Waterloo - Canada, *University of Toronto - Canada

11:00 - 12:30 SESSION 7B: Embedded Tutorial 2

Moderator: Teresa MCLAURIN, Arm Ltd. - USAZÜRICH II

-

Design and Testing Methodologies for True Random Number Generators - Towards Industry Certification

Josep BALASCH‡, Florent BERNARD*, Viktor FISCHER*, Milos GRUJIC‡, Marek LABAN#, Oto PETURA*, Vladimir ROZIC‡, Gerard VAN BATTUM♢, Ingrid VERBAUWHEDE‡, Marnix WAKKER♢, Bohan YANG‡, ‡KU Leuven - Belgium, *University of Lyon - France, #Micronic - Slovak Republic, ♢Brightside -The Netherlands

11:00 - 12:30 SESSION 7C: Special Session 2

Moderator: Nilanjan MUKHERJEE, Mentor, A Siemens Business - USAZÜRICH I

Special Session 2: Test Technologies for Safety-Critical Automotive ICs

-

In-system test for automotive SoC

Tal KOGAN, Intel Corporation - Israel -

Out with the old, in with the new: the quest to oust traditional fault models

Peter MAXWELL, ON Semiconductor - USA -

Testing AMS integrated circuits - Progressing Linearly to 0 DPPM

Andrew BRUNO, Power Integrations - USA

12:30 - 14:00 Lunch Break

FOYER

14:00 - 15:30 SESSION 8A: Test for Advanced Fault Models

14:00 - 15:30 SESSION 8A: Test for Advanced Fault Models ZÜRICH III

| Moderators: | Jedrzej SOLECKI, Mentor, A Siemens Business - USA Xiaoqing WEN, Kyushu Institute of Technology - Japan |

-

IEEE 1687 BISTs for Post-Bond Test and Electrical Analysis of High Density 3D Interconnect defects

Imed JANI, Didier LATTARD, Pascal VIVET, Lucile ARNAUD, Edith BEIGNE, Université Grenoble Alpes - France -

Interconnect-Aware Tests to Complement Gate-Exhaustive Tests

Irith POMERANZ*, Srikanth VENKATARAMAN‡, *Purdue University - USA, ‡Intel Corporation - USA -

Challenges in Cell-Aware Test

Shreyas P. DIXIT*, Divyeshkumar D. VORA*, Ke PENG‡, *Arm Embedded Technologies - India, ‡ Arm Inc. - USA

14:00 - 15:30 SESSION 8B: Embedded Tutorial 3

Moderator: Salvador MIR, Université Grenoble Alpes - FranceZÜRICH II

-

Machine learning applications in IC testing

Haralampos-G. STRATIGOPOULOS, Sorbonne University Paris - France

14:00 - 15:30 SESSION 8C: Special Session 3

Moderator: Naghmeh KARIMI, University of Maryland - USAZÜRICH I

Special Session 3: Device Aging: A Security and Reliability Concern

-

Degradation analysis of high performance industrial FinFET SRAMs

Said HAMDIOUI, Delft University - The Netherlands -

Ensuring the reliability of digital fingerprints and random numbers extracted from CMOS SRAMs as the device ages

Abhijit CHATTERJEE, Georgia Institute of Technology - USA -

Secure aging monitoring

Hans-Joachim WUNDERLICH, University of Stuttgart - Germany -

Revisiting device security regarding aging

Naghmeh KARIMI, University of Maryland - USA

15:30 - 16:00 CLOSING SESSION

ZÜRICH III

-

Closing Message

Rolf DRECHSLER, University of Bremen, DFKI GmbH - Germany

Stephan EGGERSGLUESS, Mentor, A Siemens Business - Germany -

ETS'19 Introduction

Mehdi TAHOORI, Karlsruhe Institute of Technology - Germany

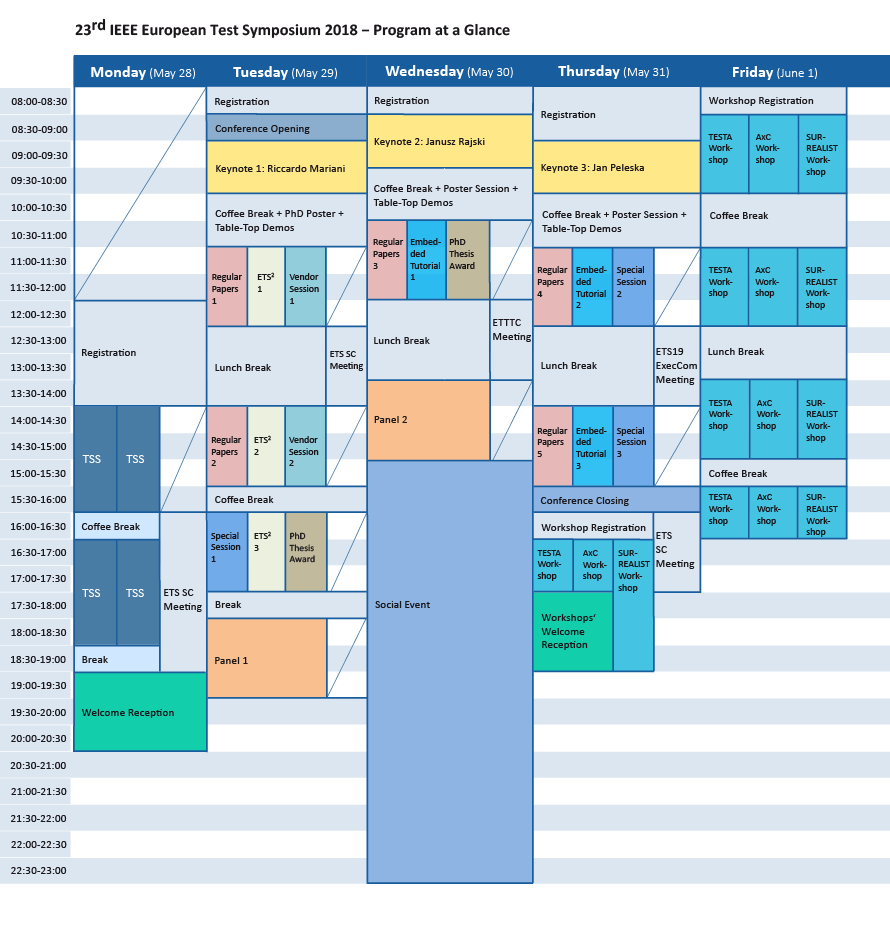

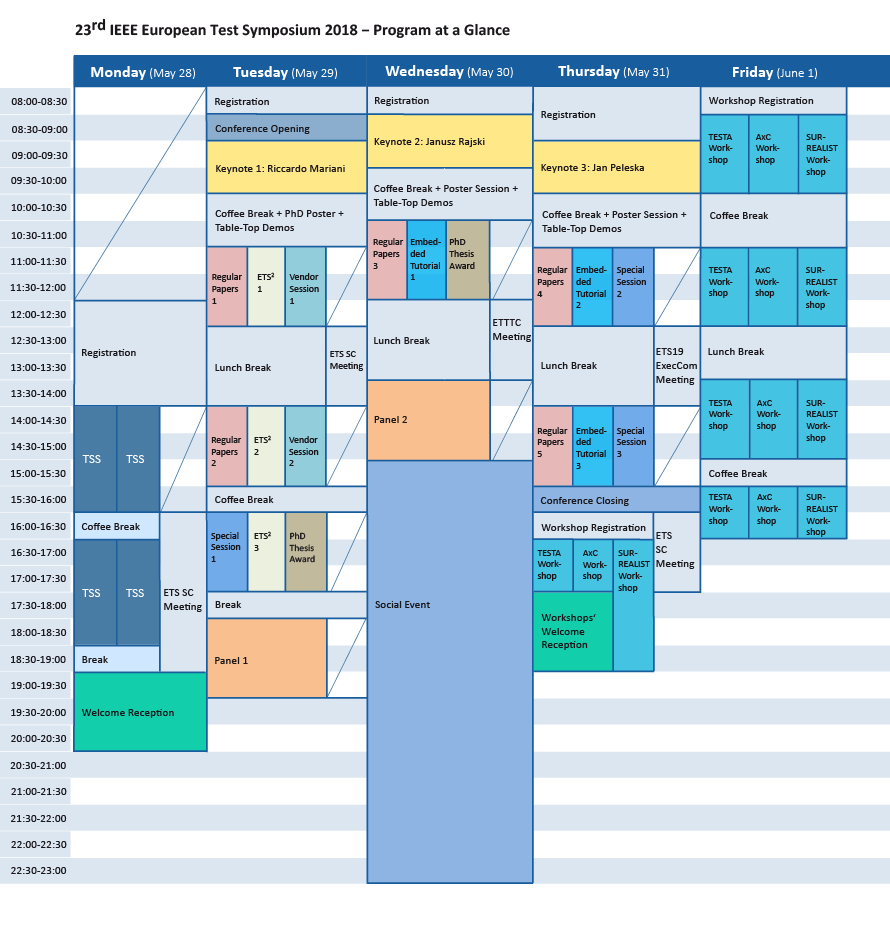

Preliminary Program at a Glance

« back to Top

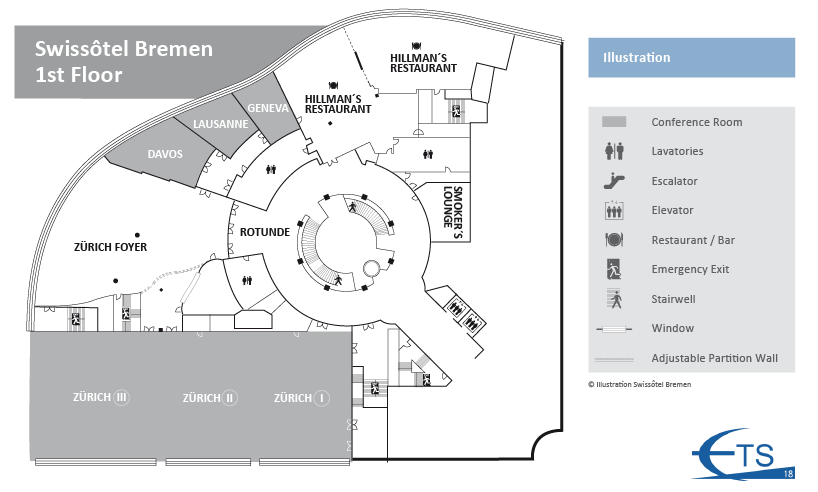

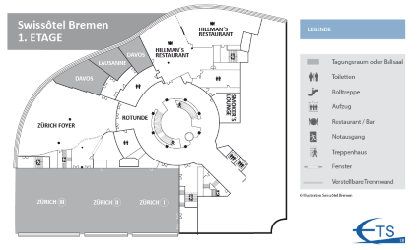

Swissôtel Bremen | 1st Floor

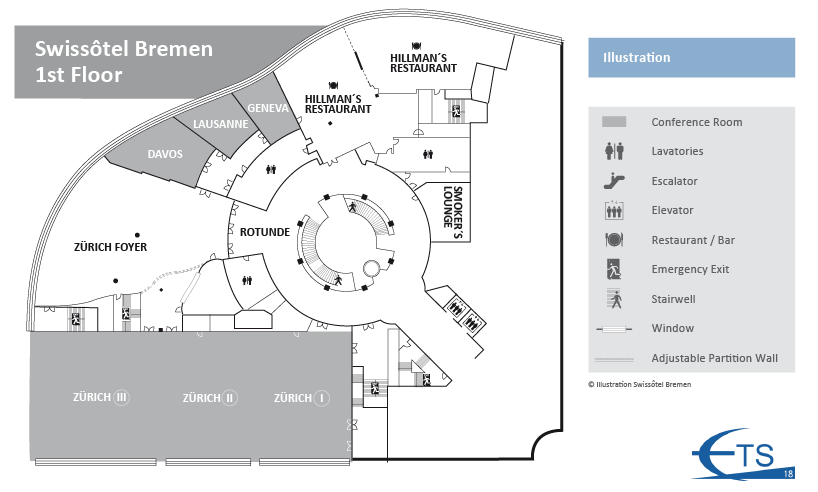

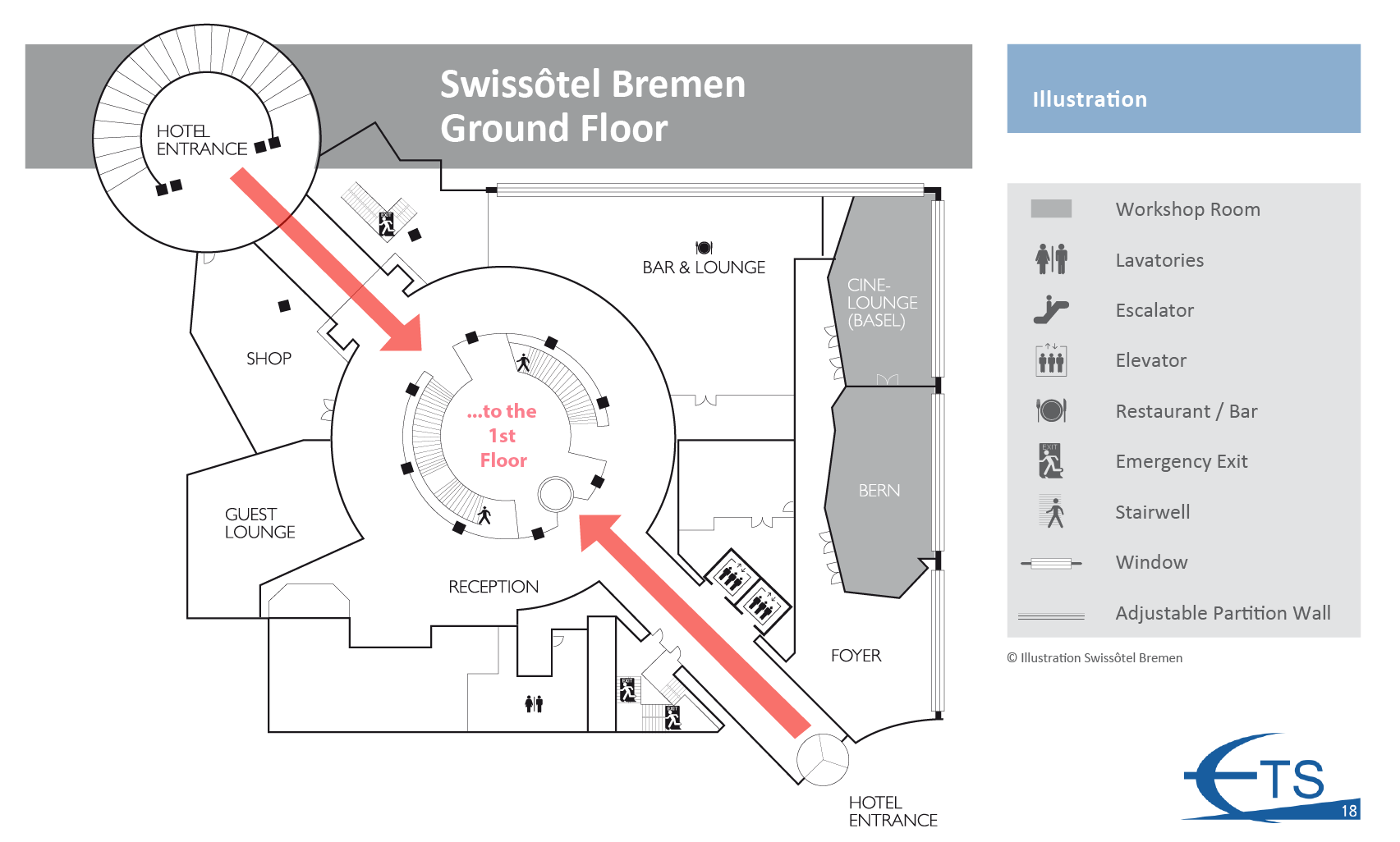

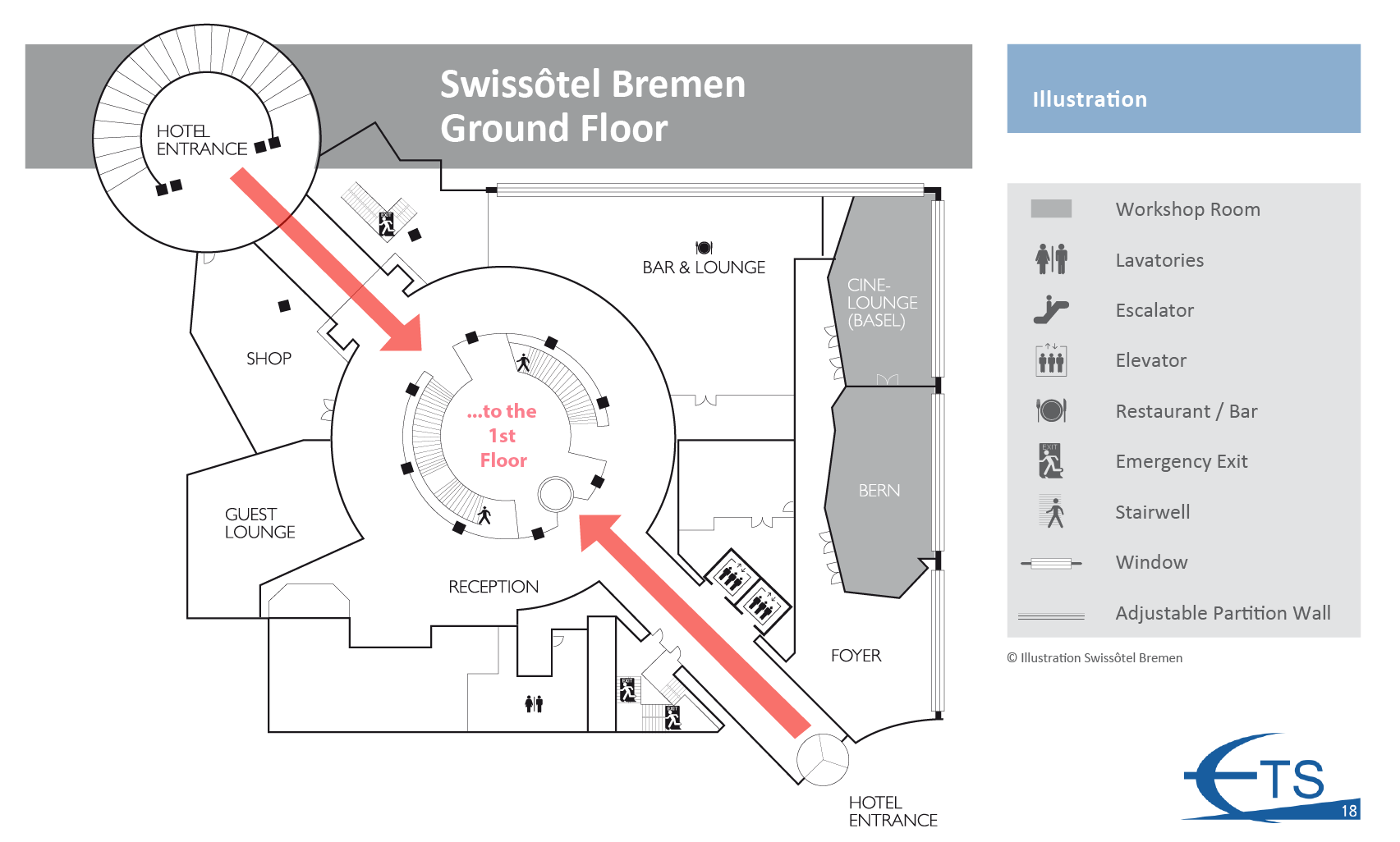

Swissôtel Bremen | Ground Floor

« back to Top

9:00 - 10:00

9:00 - 10:00  16:00 - 17:30 SESSION 3A:

16:00 - 17:30 SESSION 3A: